# **CMX635** ISDN Subscriber Processor

D/635/2 December 2001

### Features

- S/T Interface to ITU-T I.430 (TE & NT1) ISDN Terminal Equipment

- 2B + 1D-channel HDLC Controllers

- IOM<sup>™</sup>-2 / GCI Interface

- Selectable A-Law/µ-Law PCM Codec

- 100mW Speaker-Phone Output

- 2 Independent Analogue Inputs

- Pre-Programmed Tone Generators

- V.23/Bell 202 FSK Generator

- **Ringing Signal and SPM Generators**

- **DTMF Encoder/Decoder**

### **Applications**

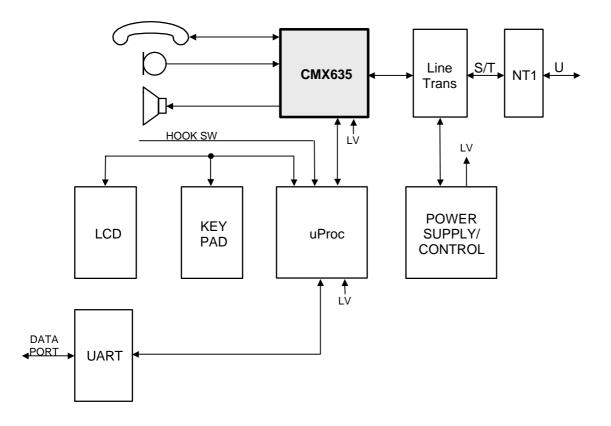

- **ISDN Intelligent NT's**

- **ISDN** Phones and Feature Phones

- **Digital & Analogue Answer-Phones**

- Data Adaptors

- Active and Passive Terminal Adaptors

- Alarm Systems

- **Point-Of-Sale Terminals**

- 'Group 4' Fax Equipment

- Video Phones

#### 1.1 **Brief Description**

The CMX635 is an integrated Subscriber Processor designed for low chip-count ISDN voice/data terminals and POTS terminal adaptors. Its functions facilitate operation in an ISDN feature phone with speakerphone capability or in a POTS terminal adapter with Subscriber Pulse Metering (SPM), DTMF encoder/decoder, Caller Line ID (CLID) and Caller ID on Call Waiting (CIDCW) capabilities. It also implements many functions needed in an intelligent NT or NT1Plus system.

The CMX635 incorporates a 4-wire ST interface conforming to ITU-T I.430 and ETS 300 012-1 specifications. HDLC Controllers and associated FIFOs are provided for B1, B2 and D-channels, which can be configured to automatically process the bit stuffing, flag generation/recognition, address matching and CRC generation/checking required to support the ITU Q.921 protocol. An IOM-2<sup>™</sup>/GCI interface is provided to enable operation with other IOM compliant devices.

The µController interface is compatible with multiplexed and non-multiplexed address/data busses and generic Motorola and Intel style control. The CMX635 will automatically detect which style of interface is being used and configure itself accordingly. The device is available in a 48pin TQFP package and has progressive powersave modes to aid low power operation.

© 2001 Consumer Microcircuits Limited

Advance Information

Section

## CONTENTS

| Page |

|------|

|      |

| 1.1 Brief Description                                                                  | 1  |

|----------------------------------------------------------------------------------------|----|

| 1.2 CMX635 Block Diagrams                                                              |    |

| 1.2.1 Functional Block Diagram                                                         |    |

| 1.2.2 Analogue Block Diagram                                                           |    |

| 1.3 Signal List                                                                        |    |

| 1.3.1 Pin numbers                                                                      |    |

| 1.3.2 Pin description                                                                  |    |

| •                                                                                      |    |

| 1.4 External Components                                                                |    |

| 1.4.2 Equivalent Analogue Input/Output Circuits                                        |    |

|                                                                                        |    |

| 1.5 Functional Description                                                             |    |

| 1.5.1 The ST interface and Digital Phase Locked Loop                                   |    |

| <ul><li>1.5.2 The HDLC Controllers and FIFOs</li><li>1.5.3 The IOM Interface</li></ul> |    |

| 1.5.4 The G.711 Codec and Analogue Gain Path                                           |    |

| 1.5.5 The Tone Generator and Tone Decoder                                              |    |

| 1.5.6 The Channel Routing Block                                                        |    |

| 1.5.7 Speaker Phone Functions                                                          |    |

| 1.5.8 The Processor Interface, Top Level Status and Power Control                      |    |

| 1.6 Programming Guide.                                                                 |    |

| 1.6.1 Interrupt Structure                                                              |    |

| 1.6.2 CMX635 Register Definition and Description                                       |    |

| 1.6.2.1 ST Interface Block                                                             |    |

| 1.6.2.2 Data Routing Block                                                             |    |

| 1.6.2.3 HDLC FIFO Control                                                              |    |

| 1.6.2.4 HDLC Rx Channel Control                                                        |    |

| 1.6.2.5 HDLC Tx Channel Control                                                        | 40 |

| 1.6.2.6 IOM Interface Control                                                          |    |

| 1.6.2.7 Clock and Power Control                                                        |    |

| 1.6.2.8 Speaker Phone Statistics                                                       |    |

| 1.6.2.9 Audio Block                                                                    |    |

| 1.6.2.10 Tone/Codec Block                                                              |    |

| 1.6.3 Register Address Definition Summary                                              |    |

| 1.7 Application Notes                                                                  |    |

| 1.7.1 Example CMX635 Configurations                                                    |    |

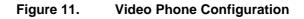

| 1.7.1.1 Dual Short Loop POTS System                                                    |    |

| 1.7.1.2 ISDN Telephone/Feature/Speaker Phone                                           |    |

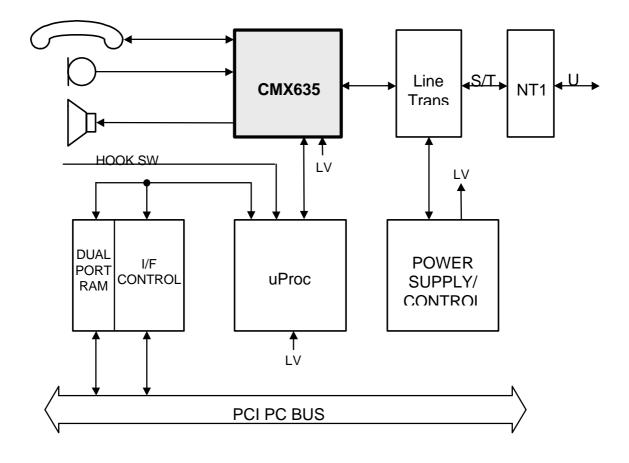

| 1.7.1.3 ISDN PC Card (Active Data Adaptor)                                             |    |

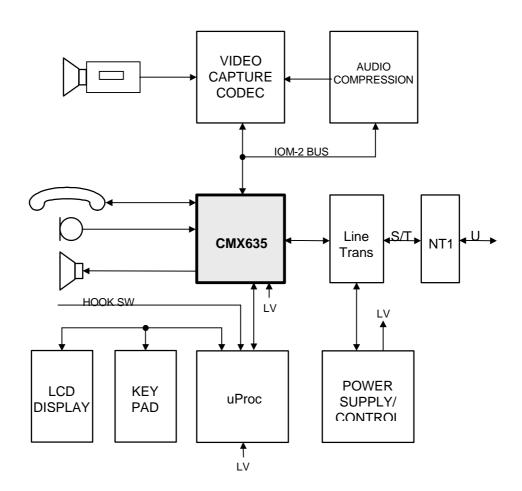

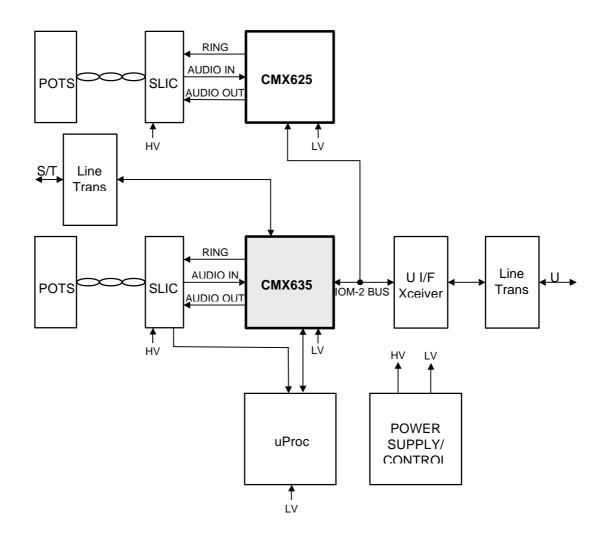

| 1.7.1.4 Video Phone                                                                    |    |

| 1.7.1.5 Intelligent NT or NT1Plus<br>1.7.2 IOM-2 Interface Summary                     |    |

| 1.7.2.1 General                                                                        |    |

| 1.7.2.2 Frame Structure                                                                |    |

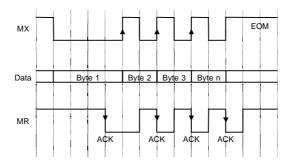

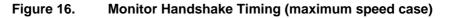

| 1.7.2.3 Monitor Channel Handshake Protocol                                             |    |

| 1.7.2.4 C/I0 Channel Description                                                       |    |

| 1.7.2.5 TIC Bus Description                                                            |    |

| 1.7.3 Tone Switching                                                                   |    |

| 1.7.4 Telecom Tones                                                                    |    |

| 1.8 Performance Specification                                                          |    |

| 1.8.1 Electrical Performance                                                           |    |

|                                                                                        |    |

| 1.8.1.2       Operating Limits    | 1.8.1 | .1 Absolute Maximum Ratings | 84 |

|-----------------------------------|-------|-----------------------------|----|

| 1.8.1.3 Operating Characteristics |       |                             |    |

|                                   |       |                             |    |

|                                   |       | Packaging                   |    |

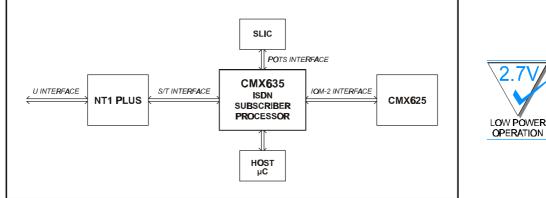

### 1.2 CMX635 Block Diagrams

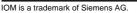

### 1.2.1 Functional Block Diagram

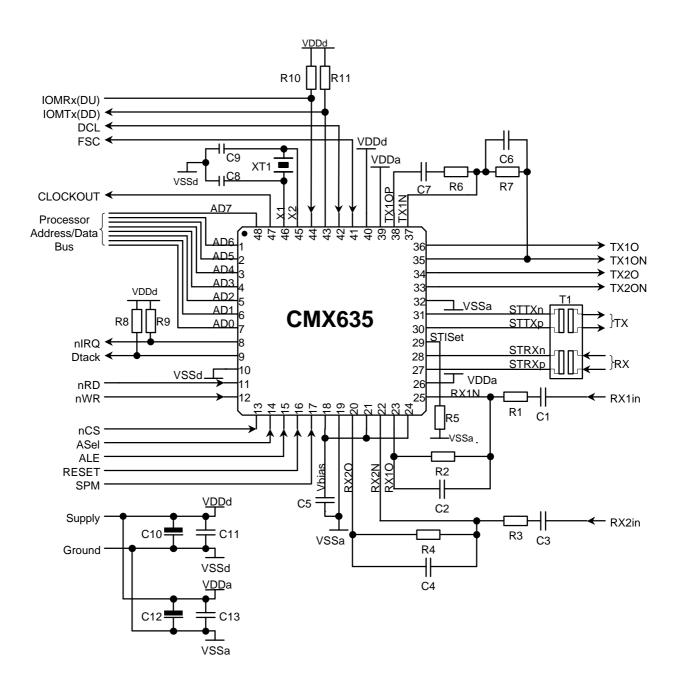

The diagram below shows the main elements of the CMX635.

RX1 and RX2 channels used for Mic or POTS input. TX1 channel used for Earpiece or POTS output. TX2 channel used for loudspeaker or POTS Ring output. For clarity, internal Processor bus not shown.

Figure 1. CMX635 BLOCK DIAGRAM

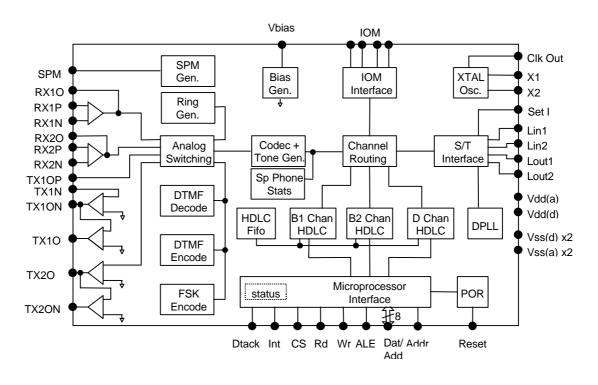

### 1.2.2 Analogue Block Diagram

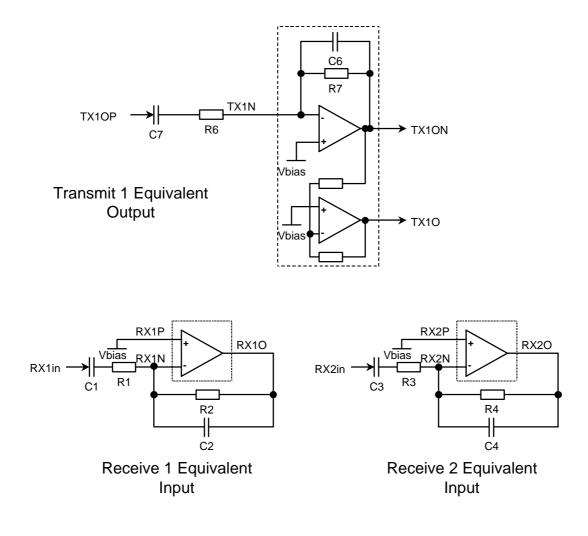

Peak to peak full scale input signal to Rx Codec is 0.986 x V<sub>DD</sub> for A-law companding, And 0.989 x V<sub>DD</sub> for  $\mu$ -law companding.

### Figure 2. ANALOGUE BLOCK DIAGRAM

### 1.3 Signal List

### 1.3.1 Pin numbers

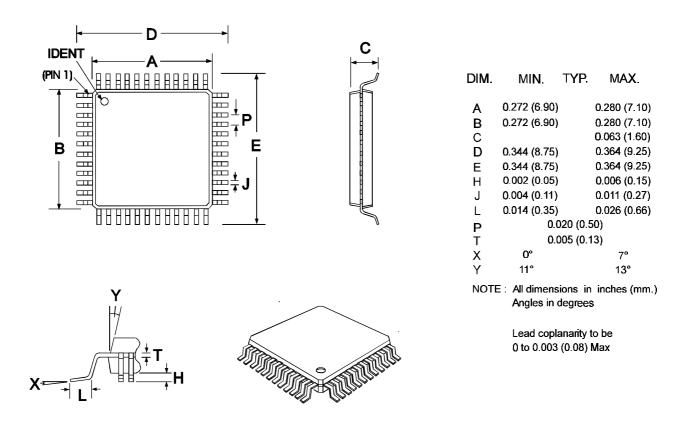

The following table lists the complete pin description of the CMX635 48-pin TFQP (L4) package.

| Pin #    | Name     | Туре                           | Function                                                                     |

|----------|----------|--------------------------------|------------------------------------------------------------------------------|

| 30       | STTXp    | Ana                            | ST interface transmit output - positive                                      |

| 31       | STTXn    | Ana                            | ST interface transmit output - negative                                      |

| 27       | STRXp    | Ana                            | ST interface receive input - positive                                        |

| 28       | STRXn    | Ana                            | ST interface receive input - negative                                        |

| 42       | DCL      | It/Oc                          | IOM-2 interface Data Clock                                                   |

| 41       | FSC      | It/Oc                          | IOM-2 interface Frame Sync                                                   |

| 43       | IOMTx    | O/D, I <sub>t</sub>            | IOM transmit output - DD when upstream device –Note 1                        |

| 44       | IOMRx    | I <sub>t</sub> , O/D           | IOM receive input - DU when upstream device – Note 1                         |

| 7        | AD0      | I <sub>c</sub> /O <sub>c</sub> | Processor Address/Data Bus bit 0 (lsb)                                       |

| 6        | AD1      | I <sub>c</sub> /O <sub>c</sub> | Processor Address/Data Bus bit 1                                             |

| 5        | AD2      | I <sub>c</sub> /O <sub>c</sub> | Processor Address/Data Bus bit 2                                             |

| 4        | AD3      | I <sub>c</sub> /O <sub>c</sub> | Processor Address/Data Bus bit 3                                             |

| 3        | AD4      |                                | Processor Address/Data Bus bit 4                                             |

| 2        | AD5      |                                | Processor Address/Data Bus bit 5                                             |

| 1        | AD6      | I <sub>c</sub> /O <sub>c</sub> | Processor Address/Data Bus bit 6                                             |

| 48       | AD7      | I <sub>c</sub> /O <sub>c</sub> | Processor Address/Data Bus bit 7 (msb)                                       |

| 14       | ASel     |                                | Address Select                                                               |

| 9        | Dtack    | O/D                            | Data Acknowledge                                                             |

| 15       | ALE      |                                | Address Latch Enable (AS in Motorola style applications)                     |

| 12       | nWR      |                                | Write Strobe (RD/nWR or E in Motorola style applications)                    |

| 11       | nRD      |                                | Read Strobe (DS in Motorola style applications)                              |

| 13       | nCS      |                                | Chip Select                                                                  |

| 8        | nIRQ     | O/D                            | Interrupt request                                                            |

| 16       | RESET    |                                | Chip Reset                                                                   |

| 46       | X1       | Ana                            | Crystal (or oscillator) input                                                |

| 45       | X1<br>X2 | Ana                            | Crystal input 2                                                              |

| 43       | CLKOUT   |                                | Clock Out - Buffered master clock                                            |

| 18       | VBIAS    | Ana                            | Internal Bias.                                                               |

| 23       | RX10     | Ana                            | Analogue input amplifier #1 output                                           |

| 24       | RX1P     | Ana                            | Analogue input amplifier #1 positive input                                   |

| 25       | RX1N     | Ana                            | Analogue input amplifier #1 negative input                                   |

| 20       | RX20     | Ana                            | Analogue input amplifier #2 output                                           |

| 20       | RX2P     | Ana                            | Analogue input amplifier #2 positive input                                   |

| 22       | RX2N     | Ana                            | Analogue input amplifier #2 positive input                                   |

| 38       | TX10P    | Ana                            | Output #1 raw output                                                         |

| 36       | TX10     | Ana                            | Output # 1 Taw output<br>Output Amplifier #1 positive output - earpiece/POTS |

| 35       | TX10     | Ana                            | Output Amplifier #1 positive output - earpiece/POTS                          |

| 37       | TX10N    | Ana                            | Output Amplifier #1 negative output - earpiece/POTS                          |

| 34       | TX20     | Ana                            | Output Amplifier #2 positive output - Loudspeaker/Ring                       |

| 33       | TX2ON    | Ana                            | Output Amplifier #2 positive output - Loudspeaker/Ring                       |

| 33<br>17 | SPM      |                                | Subscriber Pulse Metering Output                                             |

| 29       | STISet   | Ana                            | ST Tx Current Limit Set                                                      |

|          | VDDa     | Ana                            |                                                                              |

| 39       |          | S<br>S                         | Positive Analogue Supply, 2.7 - 5 V                                          |

| 26       | VDDa     | S                              | Positive Analogue Supply, 2.7 - 5 V                                          |

| 32       | VSSa     |                                | Analogue Gnd                                                                 |

| 19       | VSSa     | S                              | Analogue Gnd                                                                 |

| 40       | VDDd     | S                              | Positive Digital Supply, 2.7 - 5 V                                           |

| 10       | VSSd     | S                              | Digital Gnd                                                                  |

### **Pin Type Legend:**

| I | - | Digital Input  |

|---|---|----------------|

| 0 | - | Digital Output |

- I/O Digital Bi-directional

- O/D Open Drain

- Ana Analogue Input or Output

Subscript denotes input/output levels

- C CMOS

- T TTL

- Note 1: IOMRx normally TTL input but can become open drain output during bus reversal. IOMTx normally open drain output but can become TTL input during bus reversal.

### 1.3.2 Pin description

### STTxp, STTxn

ST bus differential transmit outputs. Upstream data in TE configuration and Downstream data in NT configuration. The nominal amplitude is  $\pm 2.1V$  differential with 280Ù load which equates to  $\pm 750$ mV at the ST interface when the recommended line transformer is used. STTxp is positive with respect to STTxn for transmission of the Frame Pulse bit.

**Note:** Particular care should be taken to avoid electro-static discharge damage to these pins as the unpowered impedance requirements result in reduced internal protection.

### STRxp, STRxn

ST bus differential receive inputs. Downstream data in TE configuration and Upstream data in NT configuration. The nominal expected differential pulse amplitude is  $\pm 1.2V$  which equates to  $\pm 750$ mV at the ST interface with recommended components. Amplitudes down to 255mV at the ST interface can be accommodated while signal activity above 100mV will generate a "Wake-up" interrupt if required. Polarity need only be maintained for point to multipoint configurations.

### DCL

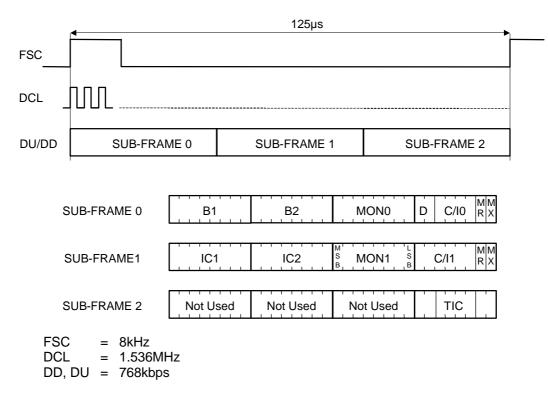

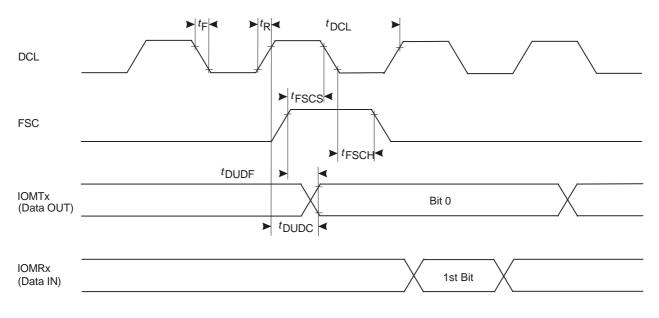

IOM-2 interface "terminal" mode data clock operating at a nominal frequency 1.536MHz. The DCL can be configured as an output (cmos levels) in timing master mode or as an input (ttl levels) in timing slave mode. DCL operates at twice the IOM bit rate and is used to sample the data on the IOM receive input.

### FSC

IOM-2 interface Frame Sync operating at a nominal frequency of 8kHz. The FSC can be configured as an output (cmos levels) in timing master mode or as an input (ttl levels) in timing slave mode. The rising edge of FSC defines the start of an IOM frame and is nominally synchronous with the rising edge of DCL.

### IOMTx, IOMRx

IOM-2 interface transmit and receive data pins operating at a nominal bit rate of 768kbps. The IOMTx pin equates to the IOM DD (Data Downstream) signal when the CMX635 is the upstream device (TE configuration) and to the IOM DU (Data Upstream) signal when the CMX635 is the downstream device (NT configuration). The IOMTx pin can be configured as open drain or active cmos level output. The direction of the IOMTx and IOMRx pins can be reversed for certain channels in the IOM frame.

### AD[7:0]

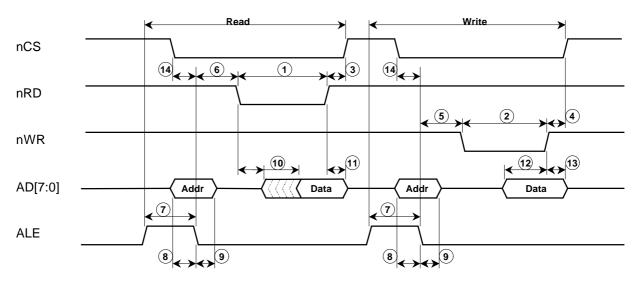

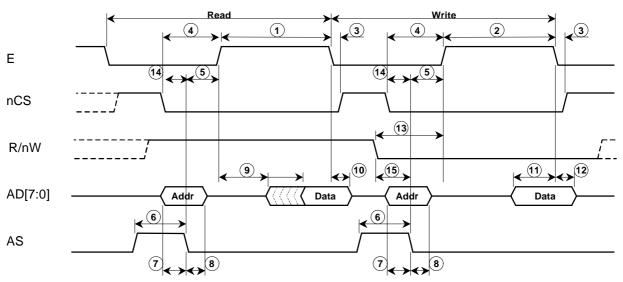

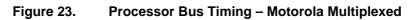

Processor interface Address/Data bus. Bi-directional cmos level input/output bus that carries multiplexed address and data when multiplexed mode is automatically detected by the CMX635 and data only when non-multiplexed mode is detected.

### ASel

Address Select. Asel, when asserted, selects the internal indirect address register as the destination for non-multiplexed processor read/writes, or the data register when de-asserted. Asel may be connected to A[0] of the non-multiplexed processor address bus. Connect to Vss for multiplexed interface operation.

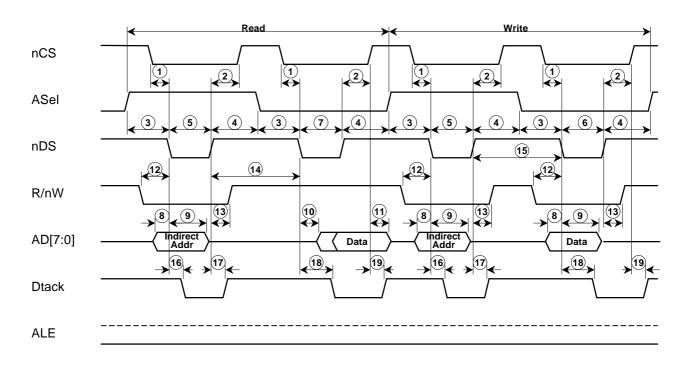

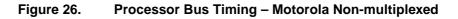

#### Dtack

Data Acknowledge. Active only when the Motorola style multiplexed mode processor interface is detected. It is an open drain output that is pulled low at the start of a processor read or write cycle and remains low until the CMX635 internal cycle is complete. The Dtack signal can be used to implement a hardware handshake cycle timing mechanism.

### ALE

Address Latch Enable. The multiplexed address from the AD bus is latched on the falling edge of ALE. Connect ALE to Vcc if an Intel style non-multiplexed interface is being used and to Vss for a Motorola style non-multiplexed interface.

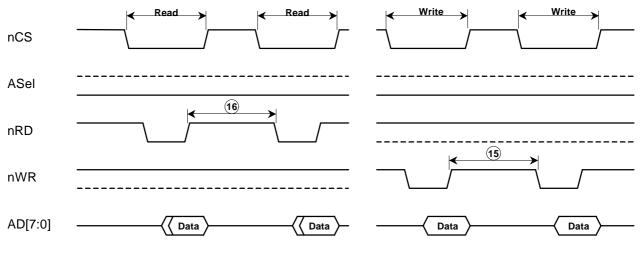

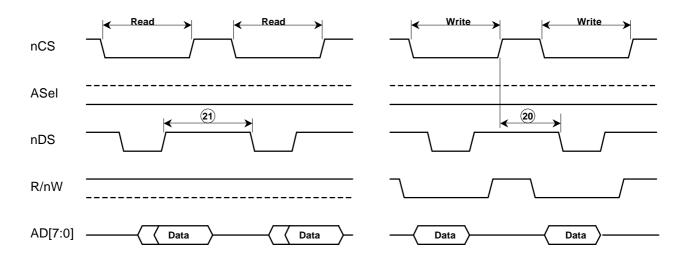

### nWR

Write Strobe, active low. Latches the data from the AD bus on the rising edge in Intel style mode. Acts as a R/nW strobe in Motorola mode. See the timing diagrams in section 1.8.1 for more details on the nWR pin function.

#### nRD

Read Strobe, active low. Initiates a CMX635 read cycle and enables read data to be driven onto the AD bus in Intel style mode. Acts as a DS or E strobe in Motorola style mode. See the timing diagrams in section 1.8.1 for more details on the nWR pin function.

### nCS

Chip Select, active low. Must be low for duration of read or write cycle in all interface modes. Processor interface is inactive and will not respond to read/write strobe activity when nCS is high.

#### nIRQ

Interrupt Request, open drain. Pulled to Vss when the CMX635 internal Status Registers generate an unmasked interrupt request. It remains in its high impedance state when no interrupts are pending. An external pull-up resistor is required.

### RESET

Global Chip Reset. Active high reset input resets CMX635 internal state and restores default configuration. The RESET input should be asserted at power-up before any configuration is written or modes activated. The RESET must be asserted until the oscillator input has stabilised (either from a crystal or external clock source) to ensure full internal reset.

### X1, X2

Oscillator input pins. A 12.288Mhz or 15.36MHz crystal may be connected between these pins (see External Components section 1.4) or an external clock source may be connected to X1 with X2 connected to Vss.

### CLOCKOUT

Buffered Clock. A buffered version of the input clock on X1 is available on CLOCKOUT and may be used for driving the clock inputs of other devices. Optionally the internal phase locked 1.536MHz clock may be routed to CLOCKOUT, which can be utilised by external circuitry to lock together multiple CMX635 devices if required.

### VBias

The internal analogue reference voltage. An external capacitor must be connected between Vbias and analogue ground to ensure noise free operation.

### RX10, RX1P, RX1N, RX2O, RX2P, RX2N

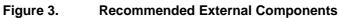

Output, positive and negative inputs of the differential microphone input amplifiers. See section 1.4.2 for details of the equivalent analogue input circuits.

### TX10, TX10N, TX1N, TX0P

Differential Outputs, negative input and internal preamplifier output of the earpiece/POTS output amplifier. See section 1.4.2 for details of the equivalent analogue output circuits. The required external gain components are inserted between the TX1ON and TX1N pins, which form the input impedance to the inverting earpiece amplifier.

### **TX2O, TX2ON**

Loudspeaker/Ring amplifier differential outputs.

### SPM

Subscriber Pulse Metering sine wave output for emulating POTS style call cost information.

### STISet

ST transmitter current set pin. A fixed resistor must be connected between this pin and analogue Vss to ensure accurate current limit on the ST transmitter.

### VSSd, VDDd, VSSa, VDDa

Analogue and Digital supply pins. Ensure adequate high and low frequency decoupling between positive and negative supplies. It is recommended that the analogue and digital supplies are locally separated.

## **1.4 External Components**

### 1.4.1 Component Values

| XT1                                                                | 12.288MHz or 15.36M                                                                             | 1Hz                                       |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------|

| T1                                                                 | Line Transformer, 2:1                                                                           | Turns Ratio i.e. ETAL P3024 - Note 1.     |

| R1, R3<br>R2, R4<br>R5<br>R6<br>R7<br>R8, R9<br>R10, R11           | Note 2.<br>110kΩ<br>15 kΩ<br>Note 3.<br>39kΩ<br>10kΩ<br>750R (5V supply),<br>470R (3.3V supply) | 1%<br>2%<br>1%<br>5%<br>5%<br>5%          |

| C1, C3, C5<br>C2, C4<br>C6<br>C7<br>C8, C9<br>C10, C12<br>C11, C13 | 1.0µF<br>220pF<br>150pF<br>27nF<br>33pF<br>1.0µF<br>10nF                                        | 5%<br>5%<br>5%<br>20%<br>10%<br>- Note 4. |

### Notes:

- 1. If a suitable transformer module is not used, protection components should be added around the line transformers, including 33R series resistors in the STTX lines and  $10k\Omega$  series resistors in the STRX lines.

- R1, R2, C1 and C2 form the gain components of input amplifier RX1. R3, R4, C3 and C4 form the gain components of input amplifier RX2. R1 and R3 should be chosen as required by the input signal level according to the following formula:

Gain = -R2/R1 or -R4/R3

C1, R1 and C3, R3 should be chosen so as not to compromise the low frequency performance.

- R6, R7, C6 and C7 form the gain components of output amplifier TX1. R6 should be chosen to give the required output signal level according to the following formula: Gain = -R7/R6

- 4. Ensure that high frequency filter capacitors are placed physically close to appropriate power pins.

### 1.4.2 Equivalent Analogue Input/Output Circuits

### 1.5 Functional Description

The CMX635 is a highly integrated ISDN Subscriber Processor that allows low chip count systems to be designed for a wide variety of ISDN voice/data terminals and POTS terminal adaptors. It can also provide the majority of functions required to implement an intelligent NT or NT1Plus system.

The CMX635 incorporates a 4-wire ST interface, which conforms fully to the ITU-T I.430 and ETS 300 012-1 specifications. It provides the necessary layer-1 control to implement both the TE and NT ends of the ST reference point and the layer-2 controls to implement the D-channel signalling layer.

HDLC Controllers and associated FIFOs are provided for the B1, B2 and D-channels. The Controllers can be configured to automatically process the bit stuffing, flag generation/recognition, address matching and CRC generation/checking required to support the ITU Q.921 protocol reducing the software overhead on the host processor. The automatic processing can be progressively disabled until fully transparent operation is achieved with corresponding increased processor load. The data FIFOs are implemented as a 1024 byte RAM that can be flexibly partitioned to form the 6 required FIFOs (2B+D, Receive and Transmit), enabling optimum FIFO size to be selected for the application.

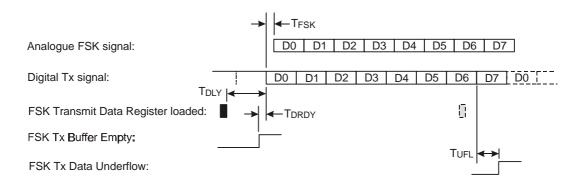

An IOM-2<sup>™</sup>/GCI interface is provided to enable operation with other IOM compliant devices. This facility can be used to connect to a 'U' Interface device in NT mode of operation or to expand the number of POTS ports in TE mode by connection to devices such as the CMX625 – ISDN TA POTS Interface. The IOM interface can be configured as a timing master or slave for TE or NT applications respectively and has full Mult-Framing capabilities.

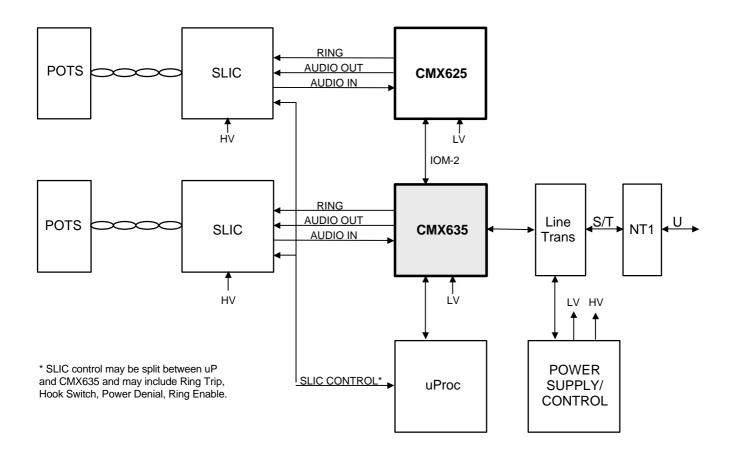

The CMX635 has the functions necessary for operation as an ISDN feature phone with speakerphone capability or as a POTS terminal adapter. There are 2 independent uncommitted differential input amplifiers suitable for connection to 2 microphones for feature-phone applications or to a SLIC/POTS hybrid for POTS operation. A 100mW power amplifier is provided to drive a speaker for feature-phones or the ring input to a SLIC for POTS. An additional output is provided to drive a handset earpiece or the SLIC/Hybrid input for POTS.

Sophisticated speakerphone operation can be implemented using the digital noise and voice filters available in the CMX635 in conjunction with user supplied software algorithms.

For POTS operation a DTMF decoder enables interpretation of dialling information and can also be configured to detect far end DTMF tones. A tone generator supplies all of the necessary tone frequencies for call progress tones. Other tone standards supported are: Fax and Modem 'answer' and 'originate', ITU (CCITT) 'R1' and 'R2' signals, and sufficient tones for simple melody generation.

Caller Line ID (CLID) and Caller ID on Call Waiting (CIDCW) functionality can be emulated using the tone generator and the FSK UART facility.

A Subscriber Pulse Metering (SPM) output is provided to enable operation with POTS legacy payphone equipment. The frequency standard can be set to either 12kHz or 16kHz.

A DTMF generator is available to allow feature-phone equipment to generate comfort dial tones and to enable control of remote DTMF signalling and Menuing systems.

The  $\mu$ Controller interface is compatible with multiplexed and non-multiplexed address/data busses and generic Motorola and Intel style control. The CMX635 will automatically detect which style of interface is being used and configure itself accordingly.

<sup>© 2001</sup> Consumer Microcircuits Limited

The CMX635 is highly configurable, via internal software accessible registers, to operate in a wide variety of applications. The details of every configuration and Status Register are described in the Programming Guide section 1.6.

The main functions of the CMX635 are shown in the block diagrams and are conceptually:

- The ST interface and Digital Phase Locked Loop

- The HDLC Controllers and FIFOs

- The IOM Interface

- The G.711 Codec and Analogue Gain Path

- The Tone Generator and Tone Decoder

- The Channel Routing Block

- Speaker Phone Functions

- The Processor Interface, Top Level Status and Power Control

#### 1.5.1 The ST interface and Digital Phase Locked Loop

The ST Interface performs the following functions:

- S/T Bus Activation/Deactivation Control

- Clock and Data Recovery

- Frame Synchronisation

- D-channel Access

- Multi-Frame Generation/Reception

The Activation/Deactivation control when configured in TE mode follows closely the ITU-T I.430 requirements and is mainly autonomous (Timer T3 requiring implementation in software). The activation states are advanced through automatic detection of the INFO0, INFO2 and INFO4 signals on the receive bus and are initiated by software writes of the Activate and Deactivate request primitives and the Power Up/Down status. Note that although the ITU specification provides no facility for the ST bus to be deactivated directly by the TE, the Deactivate Request control is provided to allow implementation of timer T3 in software. The ST activation state can be read by software and the detection of the various INFO signals can be configured to generate an interrupt if required. The activation status indicators 'Connect Indication', 'Activate Indication' and 'Error Indication' are available to the software and may also be configured to generate an interrupt request if required.

The ST interface autonomously outputs the 'INFO0', 'INFO1' and 'INFO3' signals at the appropriate states of activation/deactivation.

For NT mode of operation, the next state is under software control and is written directly to the ST interface. The detection of 'INFO0', 'INFO1' and 'INFO3' is available to the software to enable next state calculation.

The Data Recovery function consists of an analogue section and a digital section. The analogue ST receiver continuously tracks the amplitude of the incoming signal and uses an adaptive slicing level to recover digital data from the 3 level receiver input. The data is coded into positive pulse, negative pulse or no pulse. The digital section over-samples the recovered data and performs a majority decision algorithm to determine the correct recovered bit stream.

The Clock Recovery function consists of a digital phase-locked loop that tracks the raw sampled data in TE mode to produce a filtered and frequency locked master sample clock at a nominal 192kHz. This clock is used to sample the recovered receive bit stream and to generate a phase locked ST transmit clock. In NT mode the ST bit clock tracks the received IOM FSC signal thus maintaining network synchronisation.

<sup>© 2001</sup> Consumer Microcircuits Limited

The Frame Synchronisation function detects the correct occurrence of Framing and Auxiliary Framing pulses and in TE mode adjusts the receive and transmit frames accordingly. Two consecutive correctly received frames are required before the interface is designated as Frame Locked.

D-channel access in TE mode is initiated by writing the 'Data Request' primitive to the CMX635 along with the required primary priority level. The primary priority can be set to 8 for signalling frames and to 10 for data frames. The D-channel Access function will then ensure that the D-channel is available by monitoring the number of consecutive D-channel Echo bits that are set to binary 1. If the count reaches the level defined by the priority, the D-channel HDLC block is allowed to transmit. If an echo bit is received that does not match the transmitted D bit, the D-channel is released and a 'Collision' status flag is set. A 'Data Indication' primitive can be configured to generate an interrupt when the D-channel has been successfully acquired. After transmission of an HDLC frame, and if another frame is pending, the priority is automatically decreased (8 to 9 and 10 to 11) to allow other TE devices access to the D-channel. If multiple D-channel transmission frames are set up in the HDLC FIFO (see section 1.5.2) the access mechanism will automatically allow other TE's access to the D-channel between frames but will remain active until all frames are sent.

D-channel access in intelligent NT mode uses a similar access mechanism to TE mode but the D bits from the downstream TE's are used to determine D-channel activity instead of the echo bits. When an NT has successfully acquired the D-channel it sets the echo bits to the downstream TE's to binary 0, thus inhibiting TE D-channel access.

The CMX635 supports full ST Multi-framing capability and in TE mode will synchronise to incoming multi-frame markers. In NT mode formatted multi-frames are generated. The CMX635 is capable of processing 1 'Q' channel and '5' S channels as defined in ITU-T I.430. Full sets of interruptible status flags are available to indicate when the transmit/receive data buffers require servicing.

### 1.5.2 The HDLC Controllers and FIFOs

The CMX635 contains flexible Controllers and FIFOs for both B-channels and the D-channel that can be individually selected and enabled.

The main functions of the HDLC Controllers and FIFOs are:

- Flag generation/recognition

- Bit Stuffing/Destuffing and Octet Alignment

- Address Field Matching

- CRC generation/checking

- Re-configurable FIFO data buffers on all transmit and receive channels

- Multiple HDLC frame generation and Reception

The CMX635 will automatically generate the 01111110b sequence defined as an HDLC flag at the beginning of each new frame. Reception of an HDLC frame will initiate the frame receive sequence and the reception of a second flag will be interpreted as the end of an HDLC frame. 'Shared' flags (1 flag between the end of a frame and the start of a new frame) will be processed correctly in the receive channel. In the B transmit channels a 'shared' flag can optionally be used between multiple frames.

The bit stuffing and de-stuffing requirements of the HDLC protocol are automatically implemented unless the fully transparent modes of operation are selected. If transparent receive mode for a B-channel is selected, the serial bit stream is formed directly into octets and written to the receive FIFO. Transparent receive mode is not available in the D-channel. If transparent transmit mode is selected, the data from the FIFO is read in octets and transmitted directly as a serial bit stream octet aligned with the ST frame B-channel octets.

<sup>© 2001</sup> Consumer Microcircuits Limited

The address field matching function can be used in the D-channel to match incoming SAPI and TEI identifiers automatically. When address matching is turned on, incoming data frames are ignored unless the required address fields match the pre-programmed values. 4 independent match addresses can be programmed for each of the 1<sup>st</sup> and 2<sup>nd</sup> address fields as well as the broadcast addresses for both fields. The extent of address matching required can be selected to be zero, one or both fields. The combination of the pre-programmed match registers to be used is also programmable. A successful address match will set an interruptible status bit. If address matching is turned off, all incoming frames are routed to the receive FIFO irrespective of address values and the software must determine if the frame is relevant.

For transmit frames, either 1 or 2 address registers may be prepended to the transmit FIFO data automatically unless User Address mode is selected, in which case the address fields must be written to the FIFO as part of the data frame by software.

The CMX635 can automatically generate and decode the16 bit CRC fields appended to the end of HDLC frames and for received frames will generate an interruptable Good Packet or CRC Error status as appropriate. If automatic CRC handling is not required, the transmit CRC value can be supplied by the user and written as the last data octet(s) to the FIFO. For received frames the CRC value available as the last octet(s) in the receive FIFO can be decoded in software. If automatic CRC generation is enabled, a facility is provided to force a CRC error for purposes of system test/checks.

Status flags are provided to indicate a number of abnormal conditions, which can be configured to generate interrupt requests. The conditions indicated are:

- Received CRC error

- Received octet mis-alignment (frame not an integer number of octets)

- Received packet aborted (7 consecutive binary 1's received)

- Received short packet (frame length less that pre-programmed minimum)

- Transmit aborted (collision detected In the D-channel)

The CMX635 contains a FIFO, for each of the B receive and transmit channels and the D receive and transmit channel (6 total). The FIFOs are implemented as part of a 1024 byte RAM and the FIFO depths can be independently configured for each channel, in 4 byte increments, up to the 1024 byte RAM size. The sum of FIFO sizes must not exceed the 1024 byte limit. A full set of FIFO status indicators are available for each channel including 'Full', 'Empty', 'Near Full', 'Near Empty', 'Over-Write' and 'Under-Read'. The 'Near Full' and 'Near Empty' status indicate when the FIFO is 8 bytes from being full and 8 bytes from being empty respectively. The 'Full' and 'Empty' status have programmable polarity to allow for alternative interrupt generation on 'Not Full' and 'Not Empty'. Each FIFO can be individually cleared which obviates the need to read the entire FIFO if an error or abort is detected.

When a valid frame is detected the receive FIFOs are always written with all data between opening and closing flags, irrespective of the address matching and CRC checking selected.

The CMX635 HDLC controllers have extensive functionality to allow transmission and reception of multiple frames of data without processor intervention, subject to the FIFO depths set. Two methods are available for multiple frame transmission.

The first method allows multiple frames of the same length to be transmitted by writing an Octet Count register with the frame length and a Frame Count register with the required number of frames. The data to be transmitted is then written contiguously to the FIFO. When HDLC transmission is enabled, the Octet Counter (which can be read asynchronously by software) defines the FIFO data frame boundaries and decrements as each octet is transmitted. After each frame the Frame Counter is decremented to a minimum count of 1. After each frame has been

transmitted an interruptable 'Frame Complete' flag is raised and after all of the frames have been transmitted an interruptable 'All Frames Complete' flag is raised.

The second method allows for multiple frames of differing lengths to be transmitted. The number of octets in the following frame is written to the FIFO prepending the frame data. This is repeated for each frame in the multiple frame. During transmission the Octet Count is read from the FIFO and used as in method 1 above along with the pre-programmed Frame Count. After each frame the next Octet Count is loaded from the FIFO until all frames have been transmitted.

A Received Octet Counter is available to facilitate multiple frame reception. When a frame has been successfully received the software is required to respond to a Good Packet interrupt by reading and storing the Received Octet counter value. This value can then be used for reconstructing the received frame when the FIFO is eventually read. As the counter is only modulo 256, a rollover indication is provided to enable handling of long frames.

### 1.5.3 The IOM Interface

The CMX635 contains an industry standard IOM-2 interface to facilitate data transfer and programming of other IOM-2 compliant devices such as the CMX625 ISDN TA POTS Interface. A summary of the IOM-2 standard may be found in section 1.7.2 of this document.

The interface operates in Terminal Mode where 3 channels of 4 octets are transmitted per frame. The IOM-2 standard defines octets in each frame for:

- 8 bits of B1 and B2 data and 2 bits of D data.

- 8 bits of Monitor 0 data + 2 handshake bits, used for layer-1 device control functions.

- 8 bits of Monitor 1 data + 2 handshake bits, used for programming and interrogation of other IOM devices.

- 4 bits of Control/Indicate (CI) 0 data used for passing layer-1 primitives.

- 6 bits of Control/Indicate (CI) 1 data used for real time status indication between IOM devices.

- 2 8-bit channels of Inter-Communication data (IC0 & IC1) used as alternative 64kb/s data channels.

- An 8-bit TIC (Terminal IC) bus used for D-channel access from other layer-2 devices.

The IOM interface can be configured as a timing master, where the IOM clock (DCL) and the IOM frame sync. (FSC) are generated by the device, or as a timing slave where an external device provides the clock and sync. signals. Typically the CMX635 will be configured as a timing master when used in a TE system and a timing slave (taking the clock and sync signals from a U interface transceiver) in an NT system. The CMX635 always operates as a control master device.

The IOM-2 clock in terminal mode is nominally 1.536MHz giving 192 clocks per 8kHz frame, or 2 clocks per data bit. The FSC and DCL are derived from the recovered 192kHz S/T sample clock, which maintains PCM octet synchronisation. In NT mode, as a timing slave, the incoming FSC is used to synchronise the generated 192kHz S/T data.

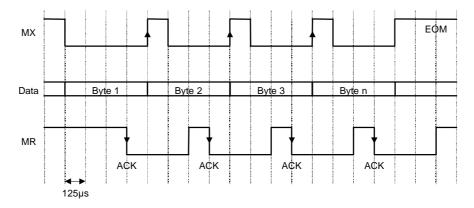

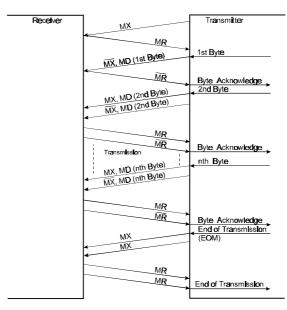

The monitor channels (0 and 1) provide a mechanism for passing programming and information octets between the master and slave IOM devices. Only 1 channel can be active at a time, the active channel being selectable from the 'IOM Monitor Channel Control' register. The monitor handshake protocol in the IOM specification is generated automatically within the CMX635 and any errors in the handshaking or received data will abort the transmit/receive sequence and raise interruptable abort flags in the 'IOM Status' register.

The operation of the B, D and IC channels is fully autonomous and they are activated by routing data to and from the appropriate channels using the 'Data Routing' registers (section 1.5.6).

Data is transmitted in the selected monitor channel by writing to the 'Monitor Channel Transmit' register when the Tx channel is idle. The 'Monitor Tx Buffer Empty' status flag will indicate when

<sup>© 2001</sup> Consumer Microcircuits Limited

another transmit octet is required. The original data octet will be retransmitted continuously until the transmit buffer is refreshed. Setting the 'Tx EOF' bit in the 'Monitor Channel Control' register when the 'Tx Buffer Empty' status flag is asserted terminates the monitor frame.

Data is received in the selected monitor channel by reading from the 'Monitor Channel Receive' register when the 'Rx Data Available' flag is asserted. The 'Rx EOF' flag indicates the end of a received IOM frame and the 'Rx Abort' flag indicates an error in reception.

The Command/Indicate channels provide a mechanism for passing "real time" layer-1 primitives (CI0) and status flags (CI1) between IOM devices. Data written to the 'CI Transmit' registers will be immediately reflected in the appropriate CI channel and will persist until the register data is changed. The received CI channel is read from the 'CI Receive' registers and 'New CI Data' flags indicate when two consecutive frames contain new and identical CI data.

The 'CI0 Transmit' register contains extra locations to enable an IOM Timing Request (TIM) to be generated and to control the Bus Activation Request (BAC) bit in the TIC channel. The TIM is used to request activation of the upstream IOM device and pulls the DU pin low from its deactivated open-drain state.

When the CMX635 is configured as a timing master, the IOM bus can be deactivated by turning off the DCL and FSC and placing the IOMTx pin in the open drain state. An IOM deactivation sequence can be optionally invoked that ensures deactivation is not completed until 4 frames of the primitive DC (Deactivate confirmation - 1111b) has been received in the CI0 channel from all downstream devices.

The CMX635 implements a sub-set of the TIC bus control functions. The TIC bus allows layer-1 control of the D-channel from other IOM devices. The CMX635 enables control of the transmitted BAC bit in NT applications when required by the U transceiver device but does not generate or monitor TIC bus addresses. In TE mode the D-channel access function will automatically operate the Stop/Go (S/G) bit to prevent other layer-1 devices from accessing the D-channel when occupied by the CMX635. The received BAC bit is monitored to establish when other layer-1 devices require access to the D-channel.

The CMX635 can be configured to reverse its Tx and Rx pin directions in the IC channels and/or the MON1 and Cl1 channels. This feature is known as "bus reversal" and enables the CMX635, when configured as a downstream IOM device, to communicate with other downstream IOM devices.

### 1.5.4 The G.711 Codec and Analogue Gain Path

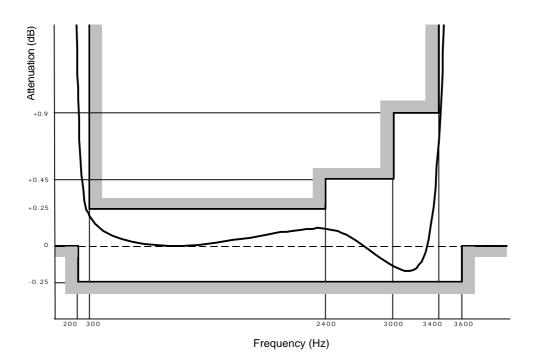

The PCM Codec-Filter performs voice digitisation and reconstruction and incorporates encoder bandpass and decoder lowpass filters with pre and post-filtering and with selectable A-law and  $\mu$ -law companding. In each case the coder and decoder process a companded 8-bit PCM word following CCITT recommendation G.711 for A-law and  $\mu$ -law conversion. The encoder bandpass filter and decoder lowpass filter provides passband flatness and stopband rejection according to CCITT recommendation G.712. The lowpass filter contains the required (Sin X)/X compensation.

Flexible receive and transmit digital gain control and analogue routing controls are provided to enable configuration into POTS or ISDN feature-phone applications.

Examples of the possible configurations for POTS are:

- Sine, Square or Trapezoid ring frequency routed to speaker output with programmable amplitude. Cadence controlled within CMX635 or externally.

- Received analogue Codec signal routed to earpiece output (SLIC/Hybrid input).

- Call progress or DTMF tones summed with or replacing Codec signal to earpiece at programmable amplitude.

- Call Waiting Tone (SAS), Caller Line ID on Call Waiting alert signal (CAS) and FSK caller ID data replacing signal to earpiece at programmable amplitude.

- Received DTMF tones from receive Codec routed to DTMF decoder for remote signalling detection.

- DTMF tones from POTS interface routed to DTMF decoder for dialled number detection.

Examples of the possible configurations for ISDN phones are:

- Input from 1 of 2 microphone inputs switchable through programmable gain to transmit Codec. Allows transducer matching and A.G.C. function for speakerphone operation.

- Independent programmable microphone channel attenuation for speakerphone algorithms.

- Received analogue Codec signal routed to earpiece and/or loudspeaker output. Loudspeaker amplifier has programmable gain for volume control and speakerphone attenuation.

- Programmable proportion of microphone channel can be added to earpiece output as "sidetone".

- DTMF tones can be routed to earpiece/speaker for dialling feedback or to transmit Codec for remote DTMF signalling.

- Full range of pre-programmed tones can be routed to speaker at programmable amplitude for ringing.

The Programming Guide, section 1.6, details the full range of routing and gain control functions available.

### 1.5.5 The Tone Generator and Tone Decoder

The Tone Generator can be used to generate tones for either DTMF tones, call progress tones, ringing signals for ISDN phones and FSK data tones for POTS caller ID functions.

The tones available are pre-programmed and grouped into 4 tone fields of up to 256 tones each. To select a particular tone or tone pair the 'Tone/Codec Control' register is first written with the required tone field and the 'Tone' register is then written with the selection from that field. The Tone Enable register allows independent power save control for the various tone types.

The Ring signal can be configured as a sine, square or trapezoidal output at a number of frequencies between 17Hz and 51Hz.

© 2001 Consumer Microcircuits Limited

D/635/2

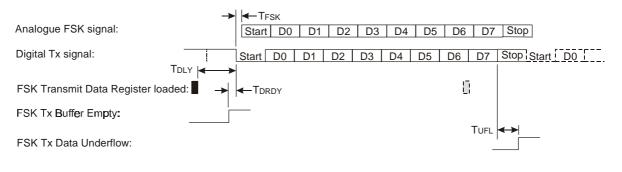

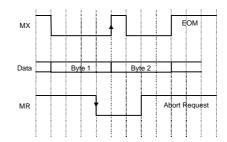

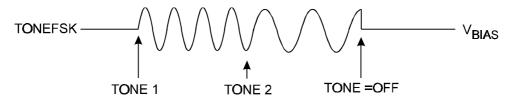

The FSK tones are automatically generated when the FSK function is enabled and FSK data is written to the transmit uart. The tone frequencies for FSK transmission can be selected to be compliant with either Bell 202 or V.23 standards.

The FSK UART can be programmed to convert the transmit data from octets to serial asynchronous data characters by adding Start and Stop bits or to transmit the octets synchronously with no start or stop bits. The baud rate is fixed at 1200 baud. Status flags indicate when the transmit buffer requires more data and whether the buffer data has underflowed (the UART has started a new FSK character before the buffer has been refreshed).

The DTMF decoder can accept a wide range of signal input amplitudes and produces a 4 bit DTMF character code that can be read from the 'DTMF Receive Data' register. Status flags indicate when a valid tone is being detected and when it ceases.

A Subscriber Pulse Metering (SPM) tone is available at a separate pin and can be programmed to 12kHz or 16kHz. When turned on, the output ramps from zero to full amplitude in approximately 4mS and ramps down again when turned off. This output allows emulation of the exchange call charging information for POTS style payphones.

### 1.5.6 The Channel Routing Block

The Channel Routing block enables the active data channels (B1, B2, D, IC1, IC2) to be flexibly routed between the ST interface, the IOM interface, the HDLC controllers and the Codec.

The available routing resources allow implementation of a full suite of loopback paths in either the transparent (the incoming data continues to be passed to the original destination as well as looping back) or the non-transparent (original source/destination for data is disabled) modes.

For B data routing, 4 prioritised routing registers are available. Each register contains a required 4-bit source and 4-bit destination port code. If there are conflicts between routing register data sources, the highest priority register routing will be implemented and the lower priority routing will be used as a destination only.

D-channel routing is contained within a single register, which is divided into high and low priority routing 4-bit nibbles. Within each nibble 2-bit source and destination port codes can be programmed. The priority mechanism works in a similar fashion to the B data routing above.

### **1.5.7** Speaker Phone Functions

The CMX635 contains comprehensive hardware filters, voice-above-noise detectors and signal path attenuators to allow a sophisticated implementation of software controlled speakerphone algorithms. The data processing is carried out on the 8kHz 8-bit wide PCM data in both the receive and transmit paths. Status bits are available to indicate the presence of voice above the background noise in both the receive and transmit channels and the amplitude of the detected voice can be read by software. The software algorithm can then decide which is the dominant channel and distribute the loop gain between receive and transmit channels.

The following data processing functions on both the receive and transmit digital data paths are provided. Note that all data processing is done on companded data in both channels.

- Full wave rectification conversion of input data

- Noise filtering of converted data with long time constant (~ 10 s)

- Speech filtering of converted data with fast attack time constant (~ 1 ms) and selectable slow decay time constant (128, 256, 500 ms).

- Auto Gated Noise Filter i.e. the statistics integration is suspended when speech is detected in the channel.

- Interrupt control system based upon filter output comparators, which provides three interrupt sources for each channel. The interrupt sources are: -

- 1) Speech filter output > noise filter output

- 2) Speech filter output > noise filter output + programmable threshold

- Speech filer output > noise filter output + programmable threshold +/hysteresis value.

- Interrupt generation when a change in any of the above conditions takes place. The user can poll the indicator flag bits to determine the exact condition that exists within the channel.

- A hysteresis register to prevent rapid and spurious interrupts when a slow noisy signal moves close to the integrated background level.

### 1.5.8 The Processor Interface, Top Level Status and Power Control

The processor interface will automatically configure itself to operate with either multiplexed or non-multiplexed address/data architectures and with generic Motorola or Intel control signals.

The processor interface type is configured after power-up by making a dummy write to the CMX635, which will monitor activity on the bus control lines and decode the appropriate interface type.

When the non-multiplexed interface is detected it is mapped as 2 addresses on the processor bus that are distinguishable by the state of the Asel pin during the read/write cycle. The first address (Asel set to binary 1) is the "indirect" address register for the following data access and must be written first. The second address (Asel = binary 0) accesses the register defined by the indirect address. Typically the single address pin (Asel) will be connected to the LSB of the processor address bus. The indirect address is persistent and, once written, can be used for further data accesses to the same address (i.e. block reads/writes to the Fifo data registers).

When the multiplexed interface is detected the internal register address is automatically demultiplexed from the AD bus and thus only single read/write cycles are required.

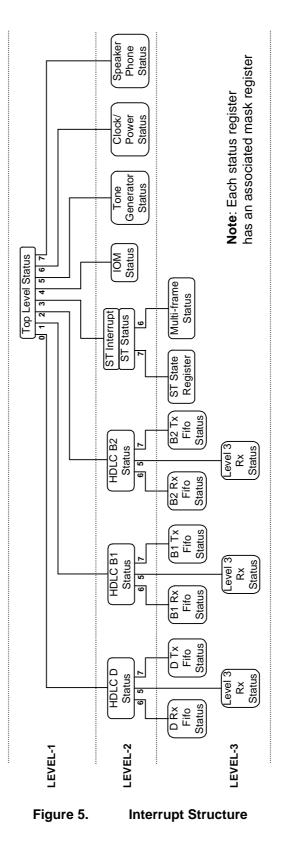

The Top Level Status register accumulates interrupt requests from the lower level blocks (as shown in Figure 5) and can be programmed to generate a selective device level interrupt request dependent on the state of the top level interrupt mask. Each lower level Status Register can be programmed to generate the interrupt requests to the top level Status Register via their own status masks. The Status Register/interrupt structure is hierarchical at 3 levels. The top level Status Register accumulates the interrupt requests from a number of level-2 Status Registers. Some of the level-2 Status Registers accumulate interrupt requests from level-3 Status Registers. To respond to an interrupt originating from a level-3 Status Register, both the top level status and the level-2 Status Registers must be read to determine the source of the interrupt.

The Power Control function includes a Clock Control register, and 3 Enable registers. The Clock Control register selects the master crystal frequency (12.288MHz or 15.36MHz), the signal routed to the CLKOUT pin (Clock In or 1.536MHz) and allows the master crystal oscillator to be disabled for complete power down applications. A hardware reset must be issued to re-enable the oscillator. The Clock Enable register can disable the system clock to individual blocks when not required thus saving power. The Tone and Audio Enable registers allow selective control of the analogue functions, Codec and tone generator/decoder, progressively reducing power consumption as un-used functions are disabled.

A Power Control Status register is available which indicates external "wake-up" events on the ST and IOM busses. Any activity on the ST bus will trigger an ST wake-up interrupt (if the interrupt is enabled with the appropriate masks), while the IOMRx pin (DU in TE applications) being pulled low will trigger an IOM wake-up interrupt. These interrupts will be generated even if the IOM and ST master clocks have been disabled.

The 'Power Control Status' register also contains 2 flags, 'CI0 Channel Idle' and 'IOM Deactivated' that indicate when the IOM bus can be safely deactivated. The 'CI0 Channel Idle'

<sup>© 2001</sup> Consumer Microcircuits Limited

status indicates that there has been 2 consecutive IOM frames received with the bus access bit set inactive (binary 1). In this condition there is no activity or pending activity in the CI0 channel. The 'IOM Deactivated' flag is valid when the IOM Deactivate sequence is in use. The flag is asserted when all downstream devices have signalled complete deactivation.

### **1.6 Programming Guide.**

### 1.6.1 Interrupt Structure

The CMX635 interrupt structure is hierarchical in nature with the interrupts from the various functional blocks converging in a top level Status Register to create a single chip level interrupt. The majority of interrupts can be interrogated from the next level of block Status Registers and a few require access to a third level of Status Registers. Each Status Register at each level can be individually masked on a bit by bit basis with its own Mask Register. Each level of Status Register is persistent, i.e. the status flags are latched and can only be cleared by reading the appropriate register. To prevent continuous interrupts from being generated the software interrupt handler should either read the interrupting Status Register or temporarily mask the appropriate bit.

The top level (level 1) Status Register comprises level-2 interrupt sources as follows.

| Bit | Interrupt Source                      | Section No. |

|-----|---------------------------------------|-------------|

| [0] | HDLC D-channel Status                 | 1.6.2.8.2   |

| [1] | HDLC B1-channel Status                | 1.6.2.8.2   |

| [2] | HDLC B2-channel Status                | 1.6.2.8.2   |

| [3] | ST Interface Status Register          | 1.6.2.1.4   |

| [4] | IOM Interface Status Register         | 1.6.2.10.5  |

| [5] | Tone Generator Status Register        | 1.6.2.14.5  |

| [6] | Clock & Power Control Status Register | 1.6.2.11.4  |

| [7] | Speakerphone Interrupt Status         | 1.6.2.12.6  |

The HDLC D, B1, B2 Status Registers and the ST Interface Status Register each have a level-3 interrupt source as detailed in the relevant sections.

The interrupt structure is shown diagrammatically in Figure 5.

Note that the reset value of the top level Status Register is the fully masked condition. For valid interrupts to be generated the top level Mask Register must be initialised early in the initialisation sequence.

| Top Level Status Register     | Addr = \$E1 | Reset = \$00 |

|-------------------------------|-------------|--------------|

| TopLevel Status Mask Register | Addr = E0   | Reset = \$00 |

### 1.6.2 CMX635 Register Definition and Description

The control registers of the CMX635 fall into the following broad categories:

- ST Interface Block

- Data Routing Block

- HDLC Fifo Control

- HDLC B1-channel Control

- HDLC B2-channel Control

- HDLC D-channel Control

- IOM Interface Control

- Clock and Power Control

- Speaker Phone Statistics

- Audio/Tone Block

- Top Level Status Register

These registers relate to the main functional blocks as defined in the functional block diagram.

Note that the clock for each block being written or read must be activated using the Clock Enable register as detailed in section 1.6.2.11.1

### 1.6.2.1 ST Interface Block

The ST Interface block registers provide the necessary primitive control for activating and reporting the status of the ST bus. They also provide the means to configure the CMX635 into its various operating modes and to control the multiframing capabilities.

The registers available in this block are:

- ST Control Register

- ST Set-Up Register

- ST Interrupt Register

- ST Status Register

- Interrupt Mask Register

- ST State Machine Register

- ST State Machine Mask Register

- MultiFrame S Register

- MultiFrame Q Register

- MultiFrame Status/Control Register

- MultiFrame Status Mask Register

- MultiFrame S Bit Counter

### 1.6.2.1.1 ST Control Register

Addr = \$80 Reset = \$00 (write/read)

The following table lists the bit functions of the ST Control Register.

| Bit | Function                    |

|-----|-----------------------------|

| [0] | Activate Request (PH-AR)    |

| [1] | Deactivate Request (MPH-DR) |

| [2] | Power Up                    |

| [3] | Unused                      |

| [4] | Data Request (PH-DATA)      |

| [5] | Priority (PH-DATA Request   |

|     | parameter)                  |

| [6] | Force Echo 0                |

| [7] | Unused                      |

Unused bits in the Control register will read back as binary 0.

The Activate Request bit equates to the PH-AR primitive and initiates ST bus activation when the CMX635 is configured in TE mode. This bit is a transient signal that advances the ST activation state machine to F4 when written with a binary 1 and reads back as binary 0.

The Deactivate Request bit equates to the MPH-DR primitive. It is a transient signal that returns the ST activation state machine to F3 when written with a binary 1 and reads back as binary 0. This control is provided to allow implementation of timer T3 in software.

The Power Up bit advances the ST activation state machine to F2 when written with a binary 1 and returns it to F1 when written with a binary 0. The status of the external power supply is expected to be indicated to the controlling processor by an external power supply monitor device.

The Data Request bit equates to the PH-DATA request primitive and is used in conjunction with the priority bit to initiate the D-channel access procedure. The access procedure is initiated when written with a binary 1 and will be maintained until the required D-channel HDLC frame(s) has been transmitted. Multiple HDLC frame transmission is possible if the D-channel frame count is set to > 1 and the required data is written to the FIFOs (see section 1.6.2.3). The current status of the Data Request bit can be read at any time. Note that for a successful D-channel frame transmission the HDLC D-channel must be correctly initialised and enabled and data routing must be established between the HDLC block and the ST interface.

The Priority bit sets the primary priority level required for a pending D-channel access. A priority of binary 0 will require 8/9 D-channel echo bits at binary 1 before access is allowed. A priority of binary 1 will require 10/11 echo bits at binary 1 before access is allowed. The secondary priority (i.e. 9 instead of 8 and 11 instead of 10) is automatically selected each time a successful access is made in accordance with ITU-T I.430.

The Force Echo0 bit may be used in NT mode to force the Echo bits transmitted downstream to binary 0. This may be required in certain loopback configurations to prevent partial D-channel access by downstream devices.

### 1.6.2.1.2 ST Set-Up Register

Addr = \$82 Reset = \$01 (write/read)

Currently only bit 0 is utilised in the Setup register.

Bit 0 is designated "TE Mode". A binary 1 written to this bit will configure the CMX635 as a TE device. A binary 0 will configure the CMX635 as an NT device. When configured as a TE device the in-built ITU-T I.430 TE activation state machine will be utilised, the reference clock timing is taken from the incoming ST bit rate, the NT-TE frame structure will be recognised and TE Multi-Framing functionality will be invoked. When configured as an NT device the activation states are under software control, the reference clock timing is taken from the IOM interface, the TE-NT generated/ recognised and NT Multi-Framing functionality will be invoked.

Bits 1 - 7 will read back as binary 0.

### 1.6.2.1.3 ST Interrupt Register/Interrupt Mask Register

| Addr = \$85 | Reset = \$00 | (read only) -  | Interrupt |

|-------------|--------------|----------------|-----------|

| Addr = \$84 | Reset = \$00 | (write/read) - | Mask      |

The ST Interrupt Register and its associated Mask Register form part of the hierarchical interrupt structure (see section 1.6.1) and provides a level-2 interrupt source to the top level Status Register. It represents an edge sensitive version of the associated ST Status Register.

Bits 0-3 of the Interrupt Register are set to binary 1 whenever the corresponding Status Register bits change (0 to 1 or 1 to 0). Bits 4 -7 are set to binary 1 only when the corresponding status bits change from binary 0 to binary 1.

All bits are reset to binary 0 when the Interrupt Register is read by software.

The Mask register will prevent the corresponding bit of the Interrupt Register from generating an ST block interrupt when set to binary 0.

### 1.6.2.1.4 ST Status Register

Addr = \$83 Reset = \$00 (read only)

The ST Status register indicates the status of the ST interface according to the definitions in the following table.

| Bit | Function                       |

|-----|--------------------------------|

| [0] | Connect Indication (MPH-II(c)) |

| [1] | Activate Indication (PH-AI)    |

| [2] | Activate Error (MPH-EI1)       |

| [3] | Data Indication (PH-DATA Ind)  |

| [4] | Collision                      |

| [5] | Unused                         |

| [6] | Multi-frame Interrupt          |

| [7] | State Machine Interrupt        |

These status bits represent a real time indication of ST interface Status. The edge-detected version is available in the ST Interrupt Register, which is used along with the Mask Register to generate ST status interrupts.

The Connect Indication bit will be set to binary 1 when the device is connected, i.e. state F3 and above. It will be reset to binary 0 when the device is in state F1 or F2.

The Activate Indication bit will be set to binary 1 when the device is activated i.e. when in state F7 or F8.

The Data Indication bit will be set to binary 1 when a pending D-channel access request has been granted and will be reset to binary 0 on completion of the frame.

The Collision bit will be set to binary 1 when a collision is detected during the D-channel access procedure. It is provided for monitoring purposes only.

The Multi-frame interrupt bit indicates a change in status of the Multi-frame block, which represents a level-3 interrupt source.

The State Machine Interrupt block indicates a change in status of the State Machine Register, which represents a level-3 interrupt source.

#### 1.6.2.1.5 ST State Machine Register/ State Machine Mask Register

| State Machine | Addr = \$87 | Reset = \$00 | U            |

|---------------|-------------|--------------|--------------|

| Mask Reset    | Addr = \$88 | Reset = \$00 | (write/read) |

The ST State Machine register forms a level-3 interrupt source (see section 1.6.1) for the level-2 ST Status register (section 1.6.2.1.4).

The ST State Machine Register provides visibility of the state of the Activate/Deactivate state machine in the ST interface and the ability to write the required state for NT mode operation. It also provides an indication of the detected INFO signals. The register bits are defined in the following table.

| Bit | Function            |

|-----|---------------------|

| [0] | State Variable [0]  |

| [1] | State Variable [1]  |

| [2] | State Variable [2]  |

| [3] | Synced              |

| [4] | INFO0 detected      |

| [5] | INFO1 detected      |

| [6] | INFO2 detected      |

| [7] | INFO3 or 4 detected |

The 3 bit state variable register can be configured to interrupt at each change of state via the SM Mask Register. In TE mode the activation/deactivation control is automatic (with the exception of expiry of T3) whilst in NT mode state transition is controlled in software by writing the appropriate code to the state variable bits. The state decoding is as follows.

| Encoding | NT State         | TE State |

|----------|------------------|----------|

| 000b     | G1               | F1       |

| 001b     | G2               | F2       |

| 010b     | G3               | F3       |

| 011b     | G4               | F4       |

| 100b     | Unused, Set to 0 | F5       |

| 101b     | Unused, Set to 0 | F6       |

| 110b     | Unused, Set to 0 | F7       |

| 111b     | Unused, Set to 0 | F8       |

The Synced bit will be set to binary 1 when the ST interface has achieved frame synchronisation.

The INFO0/1/2 bits will be set to binary 1 when the appropriate INFO signal has been detected.

The INFO3 or 4 bit will be set to binary 1 when INFO3 is detected in NT mode and INFO4 is detected in TE mode.

The SM Mask register will allow any change of state of the State Machine Register to generate an interrupt when the equivalent bit in the Mask Register is set to binary 1.

### 1.6.2.1.6 Multi-Frame S Register

Addr = \$89 Reset = \$00 (Write/Read)

All 5 defined channels of S data can be generated/received by the CMX635. The S register represents a single bit from each channel and must be written every 5 ST frames in NT Mode and read every 5 frames in TE mode. There will therefore be 4 write/reads required in 1 multi-frame (5ms) to build up the 5 channels of 4 bit S data.

The MF Status register (see section 1.6.2.1.8) indicates the start of a multi-frame and thus when the data for bit[0] of each S channel must be written/read. It also indicates when new S data is required or available and a number of other status flags.

The register bits are defined as follows.

| Bit | Function |  |

|-----|----------|--|

| [0] | SC1x     |  |

| [1] | SC2x     |  |

| [2] | SC3x     |  |

| [3] | SC4x     |  |

| [4] | SC5x     |  |

| [5] | Unused   |  |

| [6] | Unused   |  |

| [7] | Unused   |  |

### 1.6.2.1.7 Multi-Frame Q Register

Addr = \$8A Reset = \$0F (Write/Read)

The Multi-Frame Q register represents the complete 4 bits of the Q channel and is written every 20 ST frames in TE Mode and read every 20 frames in NT mode. The MF Status register (see section 1.6.2.1.8) indicates when new Q data is required or available. The Q register bits are allocated as follows

| Bit       | Function |

|-----------|----------|

| [0] (lsb) | Q1       |

| [1]       | Q2       |

| [2]       | Q3       |

| [3]       | Q4       |

| [4]       | Unused   |

| [5]       | Unused   |

| [6]       | Unused   |

| [7] (msb) | Unused   |

### 1.6.2.1.8 Multi-Frame Status Register/ Mask Register

Addr = \$8BReset = \$00(Read/Write)StatusAddr = \$8CReset = \$00(Write/Read)Mask

The Multi-Frame Status register forms a level-3 interrupt source (see section 1.6.1) for the level-2 ST Status register (section 1.6.2.1.4).

The status bits are defined in the following table.

| Bit       | Function             |            |  |

|-----------|----------------------|------------|--|

| [0] (lsb) | Tx Data Under-run    | read only  |  |

| [1]       | Rx Data Over-run     | read only  |  |

| [2]       | Tx Buffer Empty      | read       |  |

|           | only                 |            |  |

| [3]       | Rx Buffer Full       | read only  |  |

| [4]       | Start of Multi-Frame | read only  |  |

| [5]       | Multi-Frame Synced   | read only  |  |

| [6]       | Unused               |            |  |

| [7] (msb) | Multi-Frame Enable   | read/write |  |

NOTE: Tx data and Tx buffer refer to the Q data and register in TE mode and the S data and register in NT mode. Rx data and Rx buffer refer to the S data and register in TE mode and the Q data and register in NT mode.

The status bits are cleared by reading from the Status Register and, in the case of Rx buffer full and Tx buffer empty, by reading or writing the appropriate Rx/Tx register.

The least significant 6 bits of the Multi-Frame Status register are read only status bits. The most significant bit – Multi-Frame Enable – is can be written and when set to a binary 1 will enable multi-frame operation.

The Tx data under-run bit will be set to binary 1 if the Tx buffer has not been refreshed with data before new frame data is required.

The Rx data over-run bit will be set to binary 1 if new data is received before the previous data has been read from the receive buffer. The receive buffer will be overwritten with the new data.

The Tx buffer empty bit will be set to binary 1 when the data from the Tx buffer has been transferred to the multi-frame transmitter. This bit indicates the earliest that new Tx data can be loaded into the Tx buffer. In NT mode, new data must be loaded before the Tx data under-run indication (approx. 5 ST frames or 625  $\mu$ S from Tx buffer empty) or the S bit data sequence will be corrupted. In TE mode the Tx under-run indication will occur approx. 20 ST frames (2.5 mS) after the Tx buffer empty indication and the Q register will be retransmitted if the Q register is not updated.

The Rx buffer full bit will be set to binary 1 when new Rx data is available for reading. The Rx buffer must be read before the Rx over-run indication or Rx data could be lost. This will occur approx. 5 ST frames (625  $\mu$ S) after Rx buffer full in TE mode and 20 ST frames (2.5mS) in NT mode.

The start of multi-frame bit will be set to binary 1 at the earliest point that bit 1 of the 5 S data channels can be written to the S register in NT mode.

The multi-frame synced bit is set to binary 1 when the correct sequence of Fa and M bits have been detected, indicating that the multi-frame is synchronised.

### 1.6.2.1.9 Multi-Frame S Bit Counter

Addr = \$8D Reset = \$00 (read only)

The S Bit Counter indicates which of the 4 bits of the 5 SC registers is currently being received in TE mode. The counter will start at decimal 0 at the beginning of a multi-frame and count up 1 every 5 ST frames to a maximum of decimal 3. The counter aids reconstruction of the 5 SC registers.

The following table defines the bits.

| Bit   | Function                       |  |

|-------|--------------------------------|--|

| [1:0] | Binary encoded S bit count     |  |

| [7:2] | Unused, reads back as binary 0 |  |

#### 1.6.2.2 Data Routing Block

The data routing block controls the source and destination ports for the B1, B2 and D-channel data.

The available ports for B-channel data are:

- ST B1-channel

- ST B2-channel

- HDLC B1-channel

- HDLC B2-channel

- IOM B1-channel

- IOM B2-channel

- IOM IC1 channel

- IOM IC2 channel

- Codec

The available ports for D-channel data are:

- ST D-channel

- HDLC D-channel

- IOM D-channel

The B and D-channel routing is controlled by a prioritised set of 5 routing registers as follows:

| B Route Control 1 (highest priority) | Addr = \$B0 | Reset = \$00 |

|--------------------------------------|-------------|--------------|

| B Route Control 2                    | Addr = \$B1 | Reset = \$00 |

| B Route Control 3                    | Addr = \$B2 | Reset = \$00 |

| B Route Control 4 (lowest priority)  | Addr = \$B3 | Reset = \$00 |

| D Route Control                      | Addr = \$B4 | Reset = \$00 |

The 4 B and 1 D registers can all written and read.

The bit definition for all 4 B routing registers is identical and is shown in the following table.

| Bit   | Function                  |

|-------|---------------------------|

| [3:0] | Source/Destination Code A |

| [7:4] | Source/Destination Code B |

Each B-channel source/destination port is allocated a 4-bit code and the B-channel data is routed between code A and code B ports. Each route control register can have an independent pair of ports specified, but where a conflict arises with a higher priority register the lower priority port can only receive data. Specifying the same code for A and B within a single routing register will set up a loop-back.

The B-channel port codes are as follows:

| Code (hex) | Port                        |

|------------|-----------------------------|

| 0          | Off - no routing connection |

| 1          | ST B1-channel               |

| 2          | ST B2-channel               |

| 3          | IOM B1-channel              |

| 4          | IOM B2-channel              |

| 5          | IOM IC1 channel             |

| 6          | IOM IC2 channel             |

| 7          | HDLC B1-channel             |

| 8          | HDLC B2-channel             |

| 9          | Codec                       |

| A to F     | Unused – selects no routing |

### Example 1:

Route ST B1 to HDLC B2, ST B2 to Codec.

B Route Control 1 = 18h B Route Control 2 = 29h

- B Route Control 3 = 00h

- B Route Control 4 = 00h

### Example 2:

Route ST B1 to ST B1, ST B2 to ST B2, ST B1 to Codec, ST B2 to IOM IC1

B Route Control 1 = 11h B Route Control 2 = 22h B Route Control 3 = 19h B Route Control 4 = 25h